Camera ISP

Camera ISP

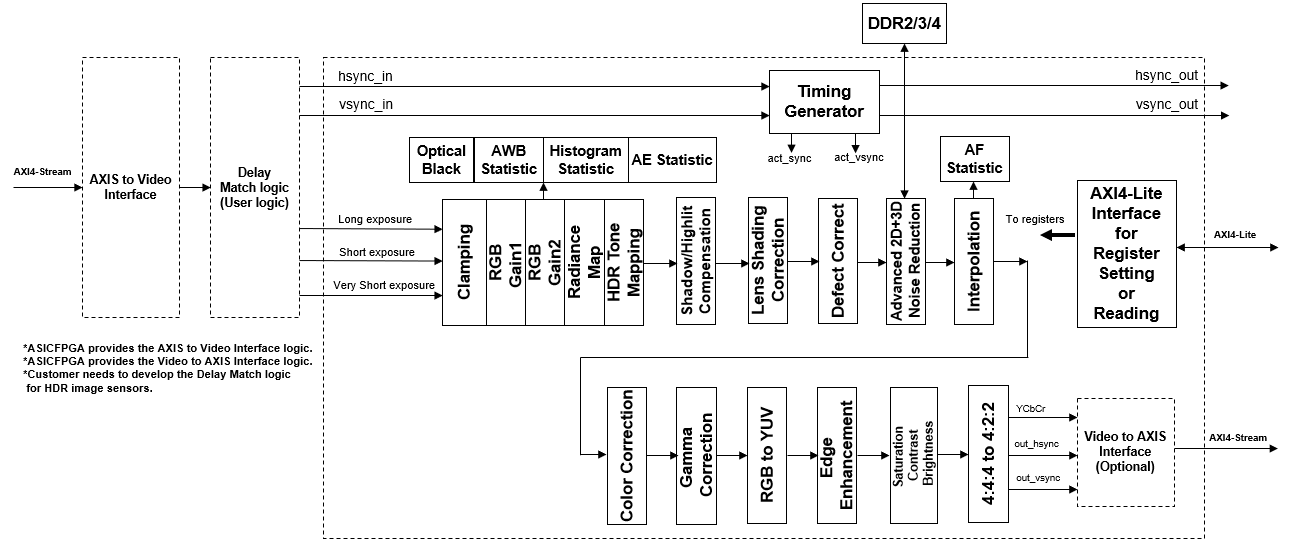

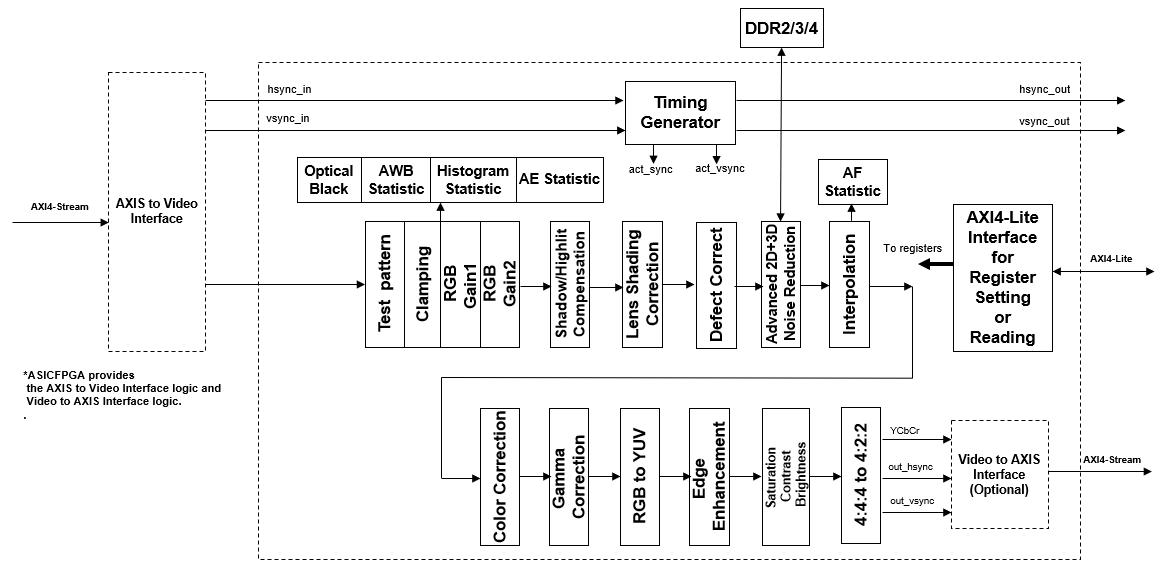

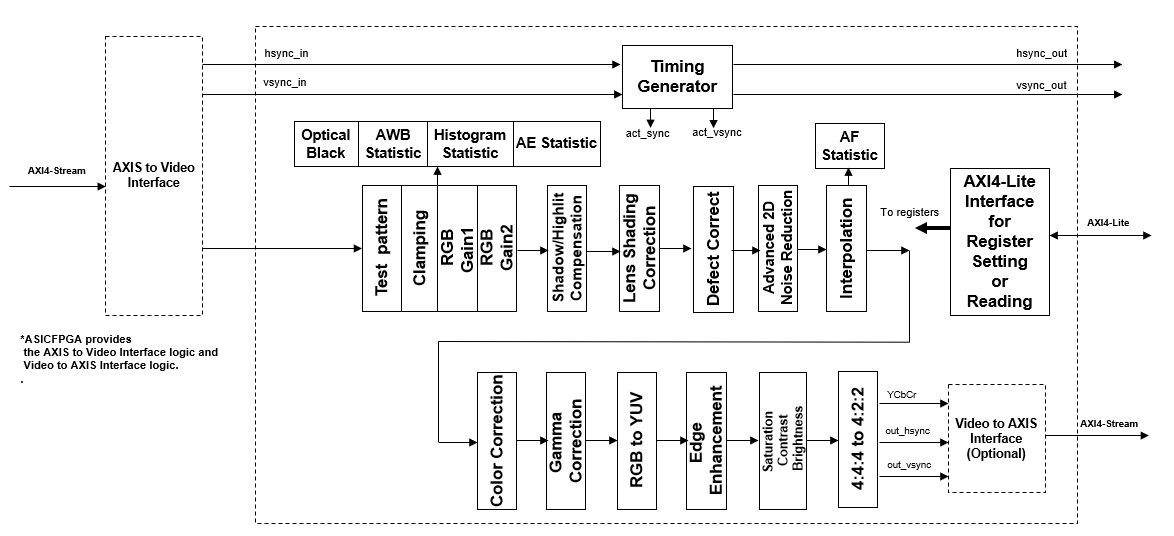

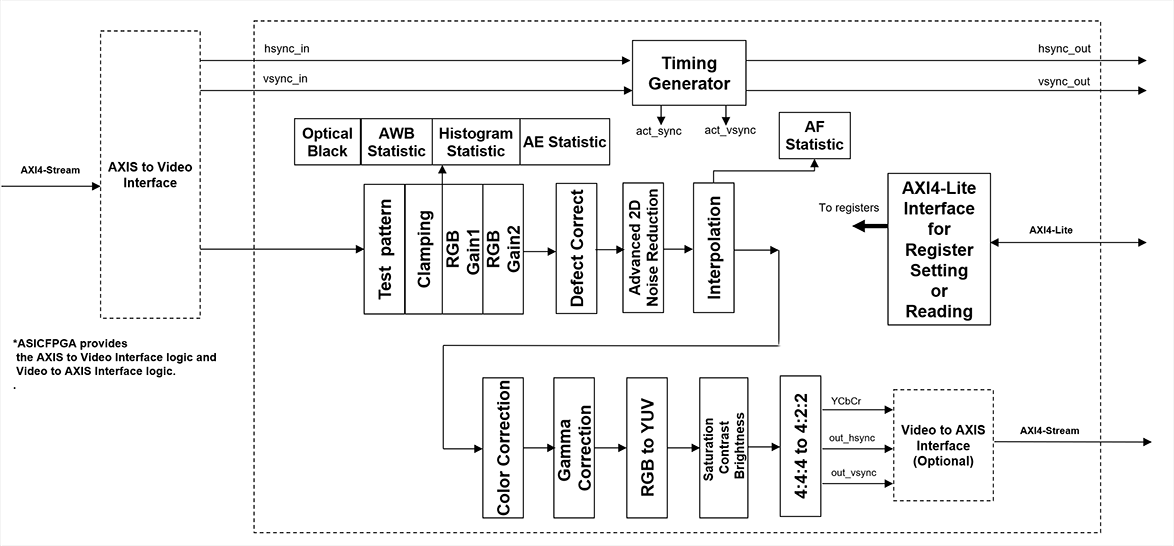

The camera image signal processing core produces high resolution, clear and sharp images by using intelligent and high-performance algorithms. The ISP core uses the minimum logic in spite of using the intelligent and complex algorithm. The ISP core is provided by Verilog source or FPGA netlist with the document and the testbench for developing FPGA and ASIC.

| Features |

|---|

| Support RGB Bayer and Monochrome image sensor |

| Support 8 ~ 14 bit Bayer data |

| Support image sensor of 256*256 ~ 8192*8192 size |

| Multiple pixel processing of 1, 2 or 4 pixels per clock |

| Support 4Kp60 and 4Kp120 at FPGA devices |

| Support for AXI4-Lite and AXI4-Stream interfaces |

| Defect Correction |

| Lens Shading Correction |

| High quality Demosaicing |

| Advanced 2D and 3D Motion Adaptive noise reduction |

| Color correction |

| Gamma correction |

| HDR processing for two or three Multiple exposure images |

| WDR (Shadow/Highlight compensation, back light compensation) |

| Edge enhancement |

| Improved dynamic range with AE of 17x15 windows and RGB Histograms |

| Improved White balance with AWB of 128x96 windows and Color temperature detection |

| Auto focus |

| Saturation, contrast and brightness control |

| Function | HDR | Star | Pro | AI |

|---|---|---|---|---|

| Clamping | ✓ | ✓ | ✓ | ✓ |

| Lens Shading correction | ✓ | ✓ | ✓ | - |

| Defect correction | ✓ | ✓ | ✓ | ✓ |

| CFA Demosacing | ✓ | ✓ | ✓ | ✓ |

| 2D+3D Noise reduction | ✓ | ✓ | - | - |

| 2D Noise reduction | - | - | ✓ | ✓ |

| Color correction | ✓ | ✓ | ✓ | ✓ |

| Gamma correction | ✓ | ✓ | ✓ | ✓ |

| RGB to YUV | ✓ | ✓ | ✓ | ✓ |

| HDR | ✓ | - | - | - |

| WDR | ✓ | ✓ | ✓ | - |

| Edge enhancement | ✓ | ✓ | ✓ | - |

| AWB, AE, AF | ✓ | ✓ | ✓ | ✓ |

| 1920x1080 60fps | 3840x2160 30fps | 3840x2160 60fps | 7680x4320 30fps |

|---|---|---|---|

| Spartan7, XC7S100-2, LUT:47K/64K | Artix-7, XC7A200T-2, LUT:94K/134K | Zynq 7000, XC7Z035-1, LUT:150K/171K | Kintex UltraScale+, XCKU3P-1, LUT:150K/162K |

| Artix-7, XC7A100T-2, LUT:47K/64K | Kintex 7, XC7K160T-1, LUT:94K/101K | Kintex 7, XC7K325T-1, LUT:150K/203K | Zynq UltraScale+, XCZU7CG-1, LUT:150K/230K |

| Zynq 7000, XC7Z030-1, LUT:47K/78K | Zynq UltraScale+, XCZU3CG-1, LUT:47K/70K | Kintex UltraScale+, XCKU3P-1, LUT:94K/162K | |

| Zynq 7000, XC7Z035-1, LUT:94K/171K | Zynq UltraScale+, XCZU5CG-1, LUT:94K/117K | ||

| Kintex UltraScale+, XCKU3P-1, LUT:47K/162K |

| 1920x1080 60fps | 3840x2160 30fps | 3840x2160 60fps | 7680x4320 30fps |

|---|---|---|---|

| Spartan7, XC7S75-2, LUT:35K/48K | Zynq 7000, XC7Z030-1, LUT:64K/78K | Zynq 7000, XC7Z035-1, LUT:111K/171K | Kintex UltraScale+, XCKU3P-1, LUT:111K/162K |

| Zynq 7000, XC7Z014S-1, LUT:35K/40K | Zynq UltraScale+, XCZU2CG-1, LUT:35K/46K | Kintex 7, XC7K325T-1, LUT:111K/203K | Zynq UltraScale+, XCZU7CG-1, LUT:111K/230K |

| Artix-7,XC7A75T-2, LUT:35K/48K | Artix-7, XC7A200T-2, LUT:64K/134K | Kintex UltraScale+, XCKU3P-1, LUT:64K/162K | |

| Kintex 7, XC7K160T-1, LUT:64K/101K | Zynq UltraScale+, XCZU4CG-1, LUT:64K/88K | ||

| Kintex UltraScale+, XCKU3P-1, LUT:35K/162K |

| 1920x1080 60fps | 3840x2160 30fps | 3840x2160 60fps | 7680x4320 30fps |

|---|---|---|---|

| Spartan7, XC7S50-2, LUT:16K/32K | Zynq 7000, XC7Z015-1, LUT:30K/46K | Zynq 7000, XC7Z030-1, LUT:55K/78K | Kintex UltraScale+, XCKU3P-1, LUT:55K/162K |

| Zynq 7000, XC7Z012S-1, LUT:16K/34K | Zynq UltraScale+, XCZU1CG-1, LUT:16K/37K | Kintex 7, XC7K160T-1, LUT:55K/101K | Zynq UltraScale+, XCZU3CG-1, LUT:55K/71K |

| Artix-7,XC7A35T-2, LUT:16K/20K | Artix-7, XC7A75T-2, LUT:30K/47K | Kintex UltraScale+, XCKU3P-1, LUT:30K/162K | |

| Kintex 7, XC7K70T-1, LUT:30K/41K | Zynq UltraScale+, XCZU2CG-1, LUT:30K/47K | ||

| Kintex UltraScale+, XCKU3P-1, LUT:16K/162K |

- FPGA level netlist

- Full functionality in with no time outs

- Original Verilog RTL source files

- Functional simulation support

- Full functionality in with no time outs